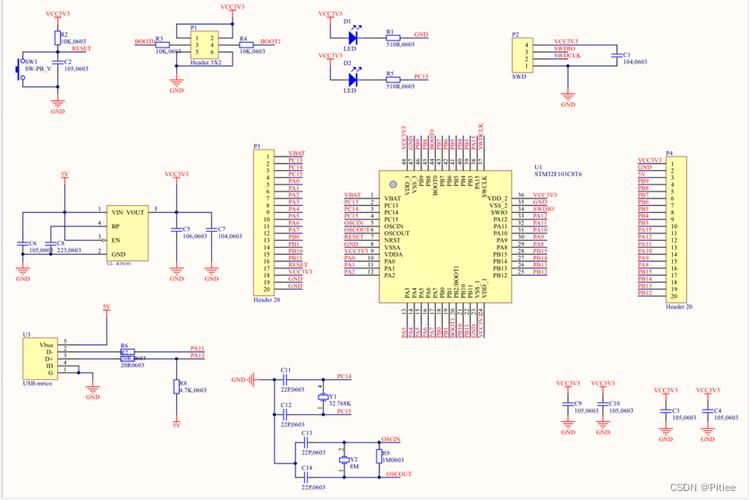

这两天 碰到的奇葩问题是 STM32定时器同步的问题。

我的设计本意是:使用定时器T3以100us的周期来定时发送命令给 FPGA。由于编码器出结果的最长时间为51us。因此,希望PWM中断要滞后于T3 约60us 。

调试过程:分别在T3和PWM中断中置IO1, IO2. 观察波形,发现IO1和IO2的周期都对,但相位差不固定,一直在变动。

百思不得其解。。。

后来,尝试用T2和T3来测试。发现相位是固定的,原来T2和T3的时钟来源是APB1 ,而T1的时钟来源是 APB2 。差异就在这里。

T8用的时钟是APB2.

改T3为T8, 相位差还是飘动。把T8由向上计数 也改成 和T1一样(中央对齐模式),这个时候相位差固定,但由之前的 55us 上升到78us 。估计和清中断标志有关。

关于中断优先级:

1. 中断优先级能分组,但只需要分一次确定下来即可,而不是分多次。若是分2组,则抢占优先级可以有0—3 这4个级别。

函数:NVIC_PriorityGroupConfig(NVIC_PriorityGroup_2);

NVIC_IRQChannelPreemptionPriority 抢占优先级,越小优先级越高

NVIC_IRQChannelSubPriority 副优先级,越小优先级越高

2. 高抢占优先级能 打断 低抢占优先级。同一抢占优先级的中断不能相互打断。

还有一个比较坑爹的情况:在调试外部中断时,怎么也进不了中断。后来查明的原因是 PE6引脚对应的中断源 为 EXTI9_5 。

大量细节都隐藏在手册里。